Objectives

-

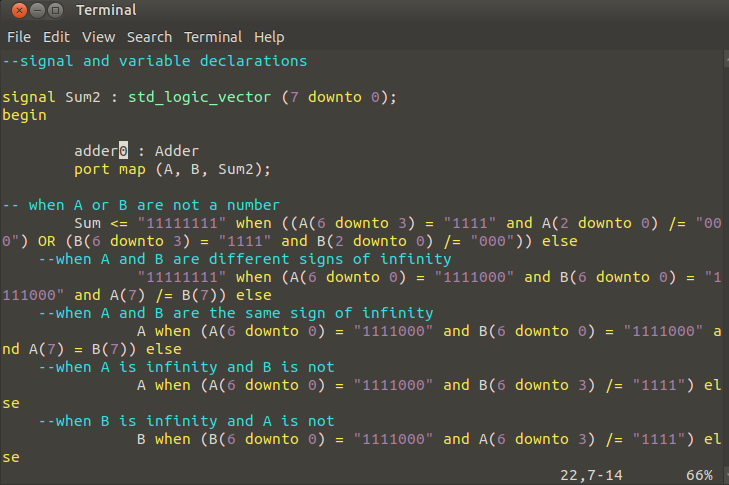

Invent a digital design that performs addition with minifloats - Must be designed in VHDL

-

The design must be a structural implementation as opposed to a behavioural one

-

The circuit must be combinational: no memory

-

The structure must be clearly identified

-

Each subcomponent must have a clear purpose

Methods/Features/Results

-

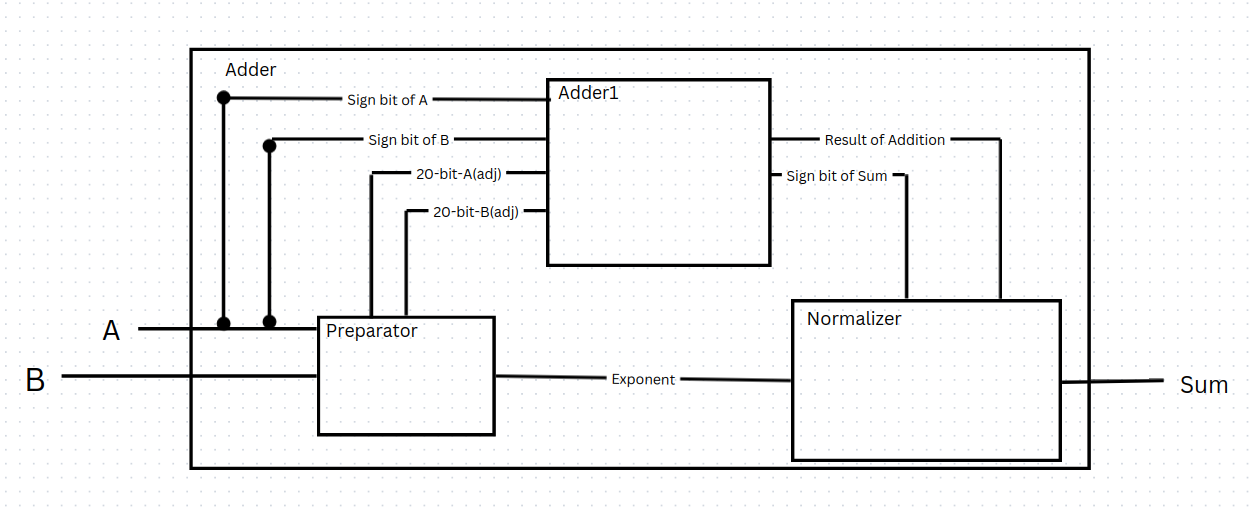

The design is separated into three main subcomponents: the Preparator, the Adder1, and the Normalizer

-

Preparator: appropriately prepares the minifloats such that mantissas can be added at the next stage

-

Adder1: computes the sum of the mantissas as a basic full adder

-

Normalizer: normalizes and truncates the sum from Adder1, combining it with the exponent from the start to yield the final result

-

Immediately identifies edge cases, avoiding unnecessary computations when possible

-

No process blocks used, avoiding the possibility of inherent memory usage